中国の復旦大学の研究チームが、従来のCMOS技術と極薄の2次元材料を組み合わせた、画期的なフラッシュメモリチップ「長筌(CY-01)」を発表しました。既存技術をはるかに凌ぐ性能と高歩留まりを実現し、「Nature」誌にも掲載されたこの技術は、未来のストレージデバイスに革命をもたらす可能性を秘めています。シリコンと2次元材料の融合という技術的困難をいかに乗り越えたのか、その詳細に迫ります。

ストレージの未来を拓く、復旦大学の新技術

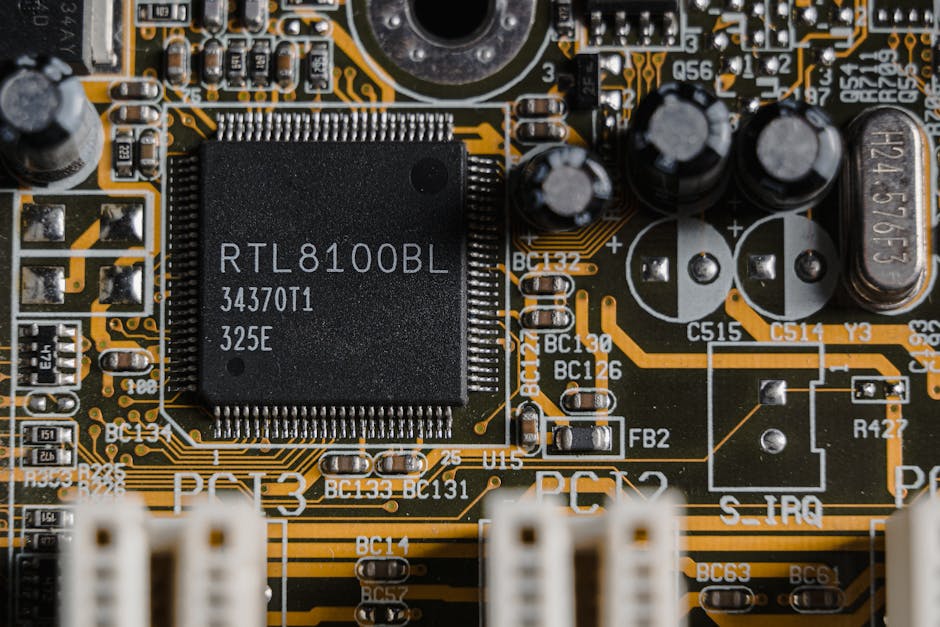

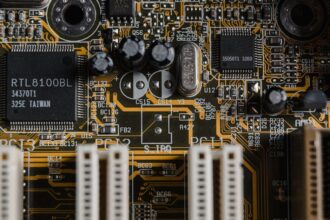

周鵬-劉春森教授率いるチームが、世界初の「2次元-シリコン基盤ハイブリッド構造フラッシュメモリチップ」を開発したことを発表しました。この研究成果は、科学誌「Nature」に掲載され、既存のFlashメモリ技術を大きく超える性能と、高い歩留まり(94.3%)を誇ります。この技術は、現在の主要な半導体製造技術であるCMOS(相補型金属酸化膜半導体)と、革新的な2次元材料を融合させることで、次世代の電子デバイスの応用サイクルを大幅に短縮し、技術革新を加速することを目指しています。

「長筌(CY-01)」アーキテクチャの秘密

究極の薄さとCMOSの融合

新たに開発された「長筌(CY-01)」アーキテクチャは、チームが以前発表した「破暁(PoX)」と呼ばれる2次元超高速フラッシュメモリデバイスと、成熟したシリコン基盤CMOSプロセスを組み合わせたものです。CMOS回路制御の2次元ストレージコアは、8-bit命令操作、32-bit高速並列操作、そしてランダムアクセスをサポートし、極めて高い性能を実現しています。

困難を乗り越えたモジュール化集積技術

この融合は容易ではありませんでした。一般的なシリコンウェハーは数百マイクロメートル厚であるのに対し、2次元半導体材料はわずか1〜3原子層という「草の葉」のように脆弱な薄さです。これらを直接積層すると、2次元材料が破損し、回路性能が実現できないという問題がありました。

復旦大学チームはこの課題に対し、モジュール化集積ソリューションという画期的な手法を採用しました。具体的には、2次元ストレージ回路とCMOS回路を別々に製造し、その後、マイクロメートルスケールのビアホール(貫通孔)を用いる高密度なチップ間相互接続技術で統合します。この革新的なプロセスにより、2次元材料とCMOS基盤を原子レベルで密接に貼り合わせることに成功し、94%を超える高いチップ歩留まりを達成しました。

未来への展望

この画期的なチップはすでに試作に成功しており、基礎研究から実際のエンジニアリング応用への大きな一歩を踏み出したことを示しています。チームは今後3年から5年かけて、この技術をギガビット級のレベルまで統合し、実験拠点を設立して産業界との連携を強化する計画です。開発される知的財産権(IP)は、提携企業にライセンス供与される予定で、これにより、データストレージ、高性能コンピューティング、IoTデバイスなど、幅広い分野での革新が期待されます。日本を含む世界の半導体産業において、この技術が新たな標準となり、私たちのデジタルライフをさらに豊かにする日が来るかもしれません。

元記事: pcd

Photo by Tima Miroshnichenko on Pexels